# Analog Frontends for Optical Communications up to 80 GBit/s

CHRISTIAN KNOCHENHAUER

#### Bibliographic information published by the Deutsche Nationalbibliothek

The Deutsche Nationalbibliothek lists this publication in the Deutsche Nationalbibliografie; detailed bibliographic data are available in the Internet at http://dnb.d-nb.de.

#### Knochenhauer, Christian

Analog Frontends for Optical Communications up to  $80\,\mathrm{GBit/s}$  ISBN 978-3-941274-75-4

#### **All Rights Reserved**

1<sup>st</sup> Edition 2011

Optimus Verlag, Göttingen

URL: www.optimus-verlag.de

Printed in Germany

Paper is FSC certified (wood-free, chlorine free and acid-free, and resistant to aging ANSI 3948 and ISO 9706)

No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, scanning, or otherwise without the prior written permission of the Publisher. Request to the Publisher for permission should be addressed to info@optimus-verlag.de.

### CHRISTIAN KNOCHENHAUER

# Analog Frontends for Optical Communications up to 80 GBit/s

Von der Fakultät Elektrotechnik und Informationstechnik an der Technischen Universität Dresden zur Erlangung des akademischen Grades

#### Doktor-Ingenieur

genehmigte Dissertation

Vorsitzender: Prof. Dr.-Ing. Eduard Jorswieck

Gutachter: Prof. Dr. sc. techn. habil. Frank Ellinger

Prof. Dr.-Ing. Andreas Thiede

Tag der Einreichung: 09.03.2011 Tag der Verteidigung: 13.05.2011

# Zusammenfassung

Die vorliegende Dissertationsschrift ist Methoden zur Steigerung von Geschwindigkeit und Leistungseffizienz von analogen Frontends optischer Hochgeschwindingkeitsdatenübertragungssysteme gewidmet. Zunächst werden theoretische Analysen der Evaluation von Kenngrößen für schnelle Breitbandschaltungen gezeigt, die gezielt auf Systemanforderungen angepasst und für den praktischen Schaltungsentwurf nutzbar sind. Die Effizienz verschiedener Frequenzkompensationsmethoden und eine neue Methode der induktiven Ausgangsanpassung bei hohen Frequenzen werden detailliert beschrieben, um daraus praktische Anwendungsrichtlinien, -grenzen und -potenziale für den Entwurf von schnellen, energieeffizienten Hochfrequenz-Breitbandschaltungen abzuleiten.

Anschließend werden die für den Schaltungsentwurf wichtigsten Integrationsaspekte diskutiert; die Simulation und Modellierung von Spulen und Leitung auf integrierten Schaltkreisen, Systemspezifikationen für optische 40 GBit/s Datenübertragungssysteme, sowie Fragen der Aufbauund Verbindungstechnik. Daraus leiten sich detaillierte Spezifikationen und genaue Simulationsmodelle aller Systemkomponenten ab, die essenziell für die aussagekräftige Simulation der Schaltungen im System sind.

Neue Methoden für den Entwurf von schnellen, leistungseffizienten Breitbandverstärkern mit hohen Ausgangsspannungshüben werden vorgestellt. Eine modifizierte Durchbruchsspannungsvervielfacherschaltung ermöglicht gleichzeitig deutliche höhere Geschwindigkeit und niedrigere Leistungsaufnahme als bisher bekannte Lösungen. Jitter-Kompromisse beim Entwurf von Eingangsverstärkern optischer Datenübertragungssysteme werden detailliert analysiert und Konsequenzen für die Optimierung von Transimpedanzverstärkern aufgezeigt.

Schaltungsbeispiele für  $40-80\,\mathrm{GBit/s}$  optische Kurzstrecken-Datenübertragungssysteme bei  $850\,\mathrm{nm}$  unterstreichen die Effektivität der obigen Methoden. Senderseitige Verstärker mit hohen Ausgangsspannungshüben bei  $40\,\mathrm{GBit/s}$  werden präsentiert, die deutlich geringere Leistungsaufnahmen als alle anderen bisher publizierte Verstärker in Silizium-Technologien aufweisen. Die vorgestellten empfängerseitigen Verstärkerschaltungen zeichnen sich, verglichen mit dem Stand der Technik, durch höhere Verstärkung, weniger Leistungsaufnahme und geringeres Rauschen aus. Schließlich wird ein  $80\,\mathrm{GBit/s}$  Breitband-Verstärker in einer  $0.25\,\mathrm{\mu m}$  SiGe BiCMOS-Technologie vorgestellt, der die Methode der induktiven Hochfrequenz-Ausgangsanpassung anwendet.

# **Abstract**

The present work studies methods of enhancing both data rates and power efficiencies of analog frontends for high-speed optical communication systems. Theoretical analyses are conducted to evaluate performance measures for high-speed broadband circuits that are adapted to system specifications and suitable for circuit design. The efficiency of frequency compensation methods, which offer power-efficient speed enhancement such as inductive peaking, feedback and Negative Miller Capacitances, as well as the method of inductive broadband output matching are analyzed in detail. For that, practical guidelines, limits and potential speed enhancements for the design of high-speed integrated broadband circuits are derived.

The integration aspects that are most important for circuit design are discussed in detail. Important aspects of simulation and modelling of onchip inductors and transmission lines, system specifications for 40 GBit/s optical data communication systems and packaging issues are considered in order to derive detailed specifications and exact system component models that make reliable system simulations for circuit design possible.

New methods for the design of power-efficient high-speed broadband amplifiers are developed. The presented modified breakdown voltage doubler topology simultaneously enables higher speed and lower power consumption. Jitter tradeoffs at receiver inputs of optical communication systems based on 850 nm multi-mode fibers are investigated in detail and consequences for the optimization of transimpedance amplifier input stages are shown.

Circuit design examples intended for use in 40 GBit/s to 80 GBit/s short-range optical communication systems at 850 nm wavelength demonstrate the efficiency of the presented methods. Several transmitter-side amplifiers delivering high-swing output voltages at 40 GBit/s while consuming significantly less power than any driver in silicon published to date are presented. The given examples of receiver-side amplifiers stand out of the state of the art in silicon transimpedance amplifiers due to their higher gain, lower power consumption and lower noise. Finally, a 80 GBit/s broadband amplifier in 0.25  $\mu m$  SiGe BiCMOS employing the method of inductive output matching is presented.

# **Contents**

| 1. | Intro | oductio | n                                                 | 1  |

|----|-------|---------|---------------------------------------------------|----|

|    | 1.1.  |         | Communication and Energy                          | 1  |

|    | 1.2.  | Optica  | al Communications Technology                      | 2  |

|    |       | 1.2.1.  | Long-Haul Transport Systems                       | 2  |

|    |       | 1.2.2.  | Short-Range Data Communication Systems            | 3  |

|    |       | 1.2.3.  | Why SiGe?                                         | 4  |

|    | 1.3.  | Scope   | and Structure of This Work                        | 4  |

| 2. | Fun   | dament  | al Methods of High-Speed Broadband IC Design      | 7  |

|    | 2.1.  | Basics  |                                                   | 7  |

|    |       | 2.1.1.  | Small- and Large-Signal Analysis                  | 7  |

|    |       | 2.1.2.  | Differential Structures – Mixed-Mode S-parameters | 9  |

|    |       | 2.1.3.  | The Problem of Complexity in High-Speed IC Design | 12 |

|    |       | 2.1.4.  | The Simplicity of Broadband Design                | 13 |

|    |       | 2.1.5.  | Kirchhoff vs. Maxwell                             | 14 |

|    | 2.2.  | Perfor  | mance Measures for Circuit Design                 | 16 |

|    |       | 2.2.1.  | Performance Measures for Communication Systems    | 16 |

|    |       | 2.2.2.  | Time-Domain Performance Measures                  | 17 |

|    |       | 2.2.3.  | Frequency-Domain Performance Measures             | 18 |

|    |       | 2.2.4.  | Case Study – Shunt Peaking                        | 19 |

|    |       | 2.2.5.  | Filter Responses                                  | 23 |

|    |       | 2.2.6.  | Conclusion                                        | 23 |

|    | 2.3.  |         | ive Peaking                                       | 24 |

|    |       | 2.3.1.  | Shunt Peaking                                     | 25 |

|    |       | 2.3.2.  | Series Peaking                                    | 28 |

|    |       | 2.3.3.  | T-coil Peaking                                    | 31 |

|    |       | 2.3.4.  | Modified T-coil Peaking                           | 34 |

|    | 2.4.  | Feedba  |                                                   | 37 |

|    |       | 2.4.1.  | Resistive Parallel Feedback                       | 37 |

|    |       | 2.4.2.  | Series Feedback – Emitter Degeneration            | 39 |

|    |       | 2.4.3.  | Negative Miller Capacitance (NMC)                 | 40 |

|    |       | 2.4.4.  | The Combination of NMC and Series Feedback $$ .   | 43 |

|    | 2.5.  |         | band Matching                                     | 45 |

|    |       | 2.5.1.  | Basics                                            | 45 |

|    |       | 2.5.2.  | Input Matching                                    | 46 |

|    |       | 2.5.3.  | Output Matching                                   | 49 |

|    |      | 2.5.4.                               | Common Peaking Methods and Output Matching         |  |  |  |

|----|------|--------------------------------------|----------------------------------------------------|--|--|--|

|    |      | 2.5.5.                               | Output Matching Using Modified T-coil Peaking $$ . |  |  |  |

| 3. | Mod  | deling o                             | of On-Chip Metallic Structures                     |  |  |  |

|    | 3.1. |                                      | mulation Fundamentals                              |  |  |  |

|    |      | 3.1.1.                               | Approach                                           |  |  |  |

|    |      | 3.1.2.                               | Meshing                                            |  |  |  |

|    |      | 3.1.3.                               | Excitation                                         |  |  |  |

|    |      | 3.1.4.                               | Circuit Element Modeling Algorithms                |  |  |  |

|    |      | 3.1.5.                               | Overall Accuracy                                   |  |  |  |

|    | 3.2. | Induct                               |                                                    |  |  |  |

|    |      | 3.2.1.                               | Two-port Inductors                                 |  |  |  |

|    |      | 3.2.2.                               | Coupled Inductors                                  |  |  |  |

|    | 3.3. | Transı                               | mission Lines                                      |  |  |  |

|    |      | 3.3.1.                               | Transmission Lines in Broadband Circuits           |  |  |  |

|    |      | 3.3.2.                               | Transmission Lines Modelling for IHP $SG25H1$      |  |  |  |

|    |      | 3.3.3.                               | Transmission Line Discontinuities                  |  |  |  |

|    | 3.4. | Bondp                                |                                                    |  |  |  |

|    |      | 3.4.1.                               | Model and Capacitance Simulation                   |  |  |  |

|    |      | 3.4.2.                               | Bondpad Geometries                                 |  |  |  |

|    |      | 3.4.3.                               | Shielding Options and Complete Models              |  |  |  |

| 4. | Syst | System Level and Integration Aspects |                                                    |  |  |  |

|    | 4.1. |                                      | ications for 40 GBit/s Communication Systems       |  |  |  |

|    |      | 4.1.1.                               | 40 GBit/s Standardization                          |  |  |  |

|    |      | 4.1.2.                               | Technical and Economical Considerations            |  |  |  |

|    |      | 4.1.3.                               | Link Budget                                        |  |  |  |

|    |      | 4.1.4.                               | Electrical Receiver and Transmitter Specifications |  |  |  |

|    | 4.2. | Electr                               | o-Optical Devices                                  |  |  |  |

|    |      | 4.2.1.                               | VCSELs                                             |  |  |  |

|    |      | 4.2.2.                               | Modulators                                         |  |  |  |

|    |      | 4.2.3.                               | Photodiodes                                        |  |  |  |

|    | 4.3. | Mount                                | ting Technologies                                  |  |  |  |

|    |      | 4.3.1.                               | Bonding                                            |  |  |  |

|    |      | 4.3.2.                               | Measurement of the Bondwire Inductance             |  |  |  |

|    |      | 4.3.3.                               | Flip-Chip                                          |  |  |  |

|    | 4.4. | Modul                                | le Packaging                                       |  |  |  |

|    |      | 4.4.1.                               | Module Overview                                    |  |  |  |

|    |      | 4.4.2.                               | Temperature Specifications                         |  |  |  |

|    |      | 4.4.3. Module Adapter Board                                | 93  |

|----|------|------------------------------------------------------------|-----|

|    |      | 4.4.4. Testboards                                          | 94  |

|    |      | 4.4.5. HF Design and Measurement Results                   | 95  |

| 5. | Opt  | ical Transmitter Frontend Integrated Circuits              | 97  |

|    | 5.1. | Breakdown Voltage Doubler Topology                         | 97  |

|    |      | 5.1.1. Breakdown Voltage of Modern Bipolar Transistors     | 97  |

|    |      | 5.1.2. Breakdown Voltage Doubler Concept                   | 98  |

|    |      | 5.1.3. Modified Breakdown Voltage Doubler Concept          | 98  |

|    | 5.2. | A 40 GBit/s Modulator Driver with High Output Swing .      | 100 |

|    |      | 5.2.1. Basic Dimensioning                                  | 101 |

|    |      | 5.2.2. Small-Signal HF Optimization of the BVD Topology    | 103 |

|    |      | 5.2.3. Large-Signal HF Optimization                        | 107 |

|    |      | 5.2.4. Output Matching and Overall Optimization Tradeoff   | 110 |

|    |      | 5.2.5. Implementation                                      | 110 |

|    |      |                                                            | 111 |

|    | 5.3. | A 40 GBit/s Driver for Vertically Integrated EO Modulators | 113 |

|    |      | 5.3.1. Application and Concept                             | 113 |

|    |      | 5.3.2. Circuit Design                                      | 114 |

|    |      | 5.3.3. Implementation and Measurement Results              | 119 |

|    | 5.4. | A 40 GBit/s Modulator Driver in 0.13 $\mu m$ BiCMOS        | 122 |

|    |      | 5.4.1. Motivation                                          | 122 |

|    |      | 5.4.2. Circuit Design                                      | 122 |

|    |      | 5.4.3. Measurement Results                                 | 125 |

|    | 5.5. | Comparison to State of the Art in High-Swing Drivers       | 128 |

| 6. | Opt  | ical Receiver Frontend Integrated Circuits                 | 131 |

|    | 6.1. |                                                            | 131 |

|    |      | 6.1.1. Packaging Model                                     | 131 |

|    |      |                                                            | 133 |

|    | 6.2. |                                                            | 135 |

|    |      | 6.2.1. Input Stage Feedback                                | 135 |

|    |      | 6.2.2. 2nd Order Analysis                                  | 139 |

|    |      | 6.2.3. Noise and Other Design Tradeoffs                    | 142 |

|    | 6.3. | A Jitter-Optimized 40 GBit/s Transimpedance Amplifier .    | 142 |

|    |      | - ,                                                        | 144 |

|    |      | 6.3.2. Output Stage Peaking                                | 145 |

|    |      |                                                            | 146 |

|    |      |                                                            | 148 |

|              | 6.4.             | Auto-Zero-Feedback in a 40 GBit/s TIA                | 151 |  |  |  |  |  |  |

|--------------|------------------|------------------------------------------------------|-----|--|--|--|--|--|--|

|              |                  | 6.4.1. Problem Scope                                 | 152 |  |  |  |  |  |  |

|              |                  | 6.4.2. Fully Integrated Low-Frequency Feedback       | 153 |  |  |  |  |  |  |

|              |                  | 6.4.3. On-Wafer Measurement Results                  | 155 |  |  |  |  |  |  |

|              |                  | 6.4.4. Measurement Results for TIA on Testboard      | 157 |  |  |  |  |  |  |

|              |                  | 6.4.5. Measurement Results for the TIA in Module $$  | 159 |  |  |  |  |  |  |

|              | 6.5.             | Linearization Tradeoffs for $40\mathrm{GBit/s}$ TIAs | 166 |  |  |  |  |  |  |

|              |                  | 6.5.1. Motivation and Specification                  | 166 |  |  |  |  |  |  |

|              |                  | 6.5.2. Circuit Design                                | 167 |  |  |  |  |  |  |

|              |                  | 6.5.3. Implementation and Measurement Results        | 170 |  |  |  |  |  |  |

|              |                  | Comparison to State of the Art in 40 GBit/s TIAs     | 176 |  |  |  |  |  |  |

|              | 6.7.             | , ,                                                  | 178 |  |  |  |  |  |  |

|              |                  | 6.7.1. Circuit Concept                               | 178 |  |  |  |  |  |  |

|              |                  | 6.7.2. Circuit Implementation                        | 178 |  |  |  |  |  |  |

|              |                  | 6.7.3. Measurement Results                           | 180 |  |  |  |  |  |  |

| 7.           | Con              | Conclusion and Outlook                               |     |  |  |  |  |  |  |

| Publications |                  |                                                      |     |  |  |  |  |  |  |

| Re           | feren            | nces                                                 | 191 |  |  |  |  |  |  |

| Lis          | sts of           | Abbreviations and Symbols                            | 201 |  |  |  |  |  |  |

| Lis          | sts of           | Figures and Tables                                   | 205 |  |  |  |  |  |  |

| Α.           | Nota             | ation and Terminology                                | 215 |  |  |  |  |  |  |

| В.           | Mea              | surement Techniques                                  | 217 |  |  |  |  |  |  |

|              |                  | Design for Testability                               | 217 |  |  |  |  |  |  |

|              |                  | Small-Signal Measurements                            | 221 |  |  |  |  |  |  |

|              |                  | Eye Diagram Measurements                             | 224 |  |  |  |  |  |  |

|              |                  | Noise Measurements                                   | 226 |  |  |  |  |  |  |

|              | B.5.             | Temperature Considerations                           | 228 |  |  |  |  |  |  |

| C.           | IHP              | SiGe BiCMOS Processes                                | 231 |  |  |  |  |  |  |

| Cι           | Curriculum Vitae |                                                      |     |  |  |  |  |  |  |

| D-           | Danksagung       |                                                      |     |  |  |  |  |  |  |

|              |                  |                                                      | 235 |  |  |  |  |  |  |

## 1. Introduction

# 1.1. Data Communication and Energy

In the last decades, the "digital revolution" and the growth of the internet have lead to a rising importance of communication technology for economy and daily life. At the same time, the ever rising energy consumption became one of the most important global challenges, with severe consequences like climate change or the increasing number of resource-related conflicts world-wide.

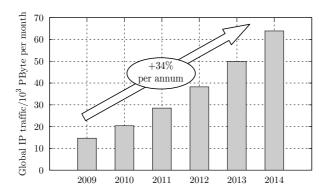

Two major technical symptoms of these developments are the global increase in telecommunication of any kind and the increase of the associated power consumption. Already in 2007, the total carbon footprint of the information technology (IT) and telecommunications industry sector amounted to 2% of the total greenhouse gas emissions from human activity – that is as much as the footprint of the civil aviation sector [Smart10, Brunschwiler09]. In the next 5 years, the global internet traffic (IP traffic) is forecasted to increase by 34% annually as depicted in Figure 1.1 [Cisco10]. It is evident that more power-efficient computing and telecommunication technology is a key for future economic prosperity and human development.

As for telecommunications, there are two main levers that can be used to increase system energy-efficiency: an increase in the data rate of the systems and the reduction of power consumption per system. However,

Figure 1.1: Global internet (IP) traffic prediction 2009-2014. [Cisco10]

2 1. Introduction

these levers are only effective if they go along with cost-efficiency and wide-spread application of the systems. In this context, the present work deals with analog frontends for optical communications. All methodologies, circuits and applications presented herein reflect the ever-challenging tradeoff between data rate, power consumption and cost considerations.

# 1.2. Optical Communications Technology

Optical communication systems as shown in Figure 1.2 have a very broad range of applications. In the past, they were exclusively employed in long-haul telecommunications because technological efforts and costs for these systems were very high. During the last decade, with increasing data rates and new technologies such as Vertical Cavity Surface Emitting Lasers (VCSELs), optical communication systems have become more and more energy and cost-efficient as compared to copper-based solutions even for short transmission distances. Due to the specific demands in the application fields, two separated, nearly completely different technologies for long-haul and short-distance communications have emerged.

#### 1.2.1. Long-Haul Transport Systems

Long-haul transport systems are used to transmit big amounts of aggregated data over long distances, ranging from 1 km up to several thousand kilometers. The main limiting technological factor is the optical signal integrity in the fiber over those distances. Considerable conceptual and technical effort is undertaken to compensate signal degradation, such as dispersion-compensated fibers or optical amplifiers. Economically, the installation of the fibers in the field is the most important cost factor. Technological efforts and costs for the electrical system components are far less important. Consequently, the main challenge in system design remains to get the highest possible performance per fiber. The choice of technologies is therefore mainly performance-based. This motivates, for example, the use of cost-intensive III-V semiconductor technologies for the integrated circuits (ICs) because of their superior gain and noise characteristics, the use of single-mode fibers at 1300 nm or 1550 nm wavelength for their superior dispersion properties, or the employment of avalanche photodiodes and the considerable effort for stabilizing their supply voltages >100 V.

Figure 1.2: Typical structure of an optical communication system.

### 1.2.2. Short-Range Data Communication Systems

Typical applications for short-range data communication systems include connections between servers in big data centers or networking connections in buildings. Low cost and installation efforts are key requirements for such systems. Thus, multi-mode optical fibers with higher core diameter and VCSELs at 850 nm are used to lower mechanical packaging tolerance requirements and implementation cost. For the electrical path, silicon-based semiconductor technologies are primary choice. These technologies intrinsically have less performance than the resource-limited III-V technologies<sup>1</sup> typically used in long-haul transport systems, but are much more cost-efficient in high volume production. Technological drawbacks such as the high dispersion of multi-mode fibers, the low extinction ratios

<sup>&</sup>lt;sup>1</sup>As silicon is available in abundance, setup and mask costs are predominant for silicon technologies. Main cost factor in III-V technologies are raw materials such as Indium or Gallium.

<sup>&</sup>lt;sup>2</sup>APC: automatic power control, AGC: automatic gain control

4 1. Introduction

of fast VCSELs at 850 nm or the higher noise of SiGe IC technologies have to be compensated by system concept and component design. In addition, power consumption becomes a key economical and ecological factor because of the high number of parallel systems found in typical applications. In a data center for example, power consumption is a main cost factor and the biggest efficiency lever for improving efficiency. Reducing power consumption of one system leads to multiple additional power and cost savings in cooling.

The main challenge in circuit design for short-range data communication systems is therefore twofold. On the one hand, signal integrity has to be assured in spite of limited performance of underlying technologies. On the other hand, power consumption has to be reduced as far as possible. Typical tradeoffs in common circuit topologies exchange power consumption against signal quality. Thus, short-range data communication systems feature a huge need and also a huge potential for conceptual performance and efficiency improvements through circuit design.

### 1.2.3. Why SiGe?

The choice of semiconductor technology is closely linked to the intended application and vital to circuit design. As discussed in the previous section, only silicon-based technologies are suitable for cost-sensitive, potential mass-market applications. There are two major options for high-frequency circuits; CMOS and SiGe. The former offers cost advantages in mass production and less power consumption, especially for low-frequency and digital circuits. SiGe Heterojunction Bipolar Transistors (HBT), however, have much better noise characteristics and more gain at higher frequencies provided a comparable lithography [Ellinger07]. They are therefore primary choice for prototypes of next-generation communication applications like the circuits presented in this work.

# 1.3. Scope and Structure of This Work

This work studies methods of enhancing both data rate and power efficiency of analog frontends for high-speed optical communication systems. Broadband amplifier circuit design examples intended for application in  $40\,\mathrm{GBit/s}$  to  $80\,\mathrm{GBit/s}$  short-range optical communication systems at  $850\,\mathrm{nm}$  wavelength are given in order to demonstrate the efficiency of the presented methods.

Chapter 2 gives a short introduction in theoretical basics of high-frequency circuit design. Details and extensions of the theory are presented in two major points vital to the enhancement of data rates and power efficiency; the speed enhancements of integrated circuits using frequency compensation methods such as inductive peaking or Negative Miller Capacitances (NMCs) and the output matching of broadband circuits at high frequencies. The potential and optimization algorithms of those methods are studied in detail.

As analog frontends are located at the periphery and directly at the interface between optical and electrical path of the system, integration aspects are of high importance for circuit design. In Chapter 3, details on the modelling of on-chip passive elements are discussed. This spans from inductors and transmission lines to the consequences for the implementation of the methods presented in Chapter 2. Chapter 4 provides details about system aspects such as standardization, external elements and electro-optical interfaces. Key parameters and models are derived in order to provide specifications for the optical frontend integrated circuits presented in the following chapters.

Chapter 5 presents circuits for optical transmitter frontends. One of the main topics in this field are methods to generate voltage swings beyond the breakdown voltage of the bipolar transistors at very high speeds. This has become important because breakdown voltages of modern, aggressively scaled semiconductor technologies are decreasing with further miniaturization of devices while optical modulators require high input voltage swings for high-speed operation. Several implementations of low-power high-speed modulator drivers for different applications and in different technologies are presented.

Chapter 6 deals with design methods and implementations for optical receivers. Several fundamental problems such as jitter optimization of receivers employing high-capacitance multi-mode photodiodes or linearization methods for coherent receiver frontends are discussed in detail. Circuit designs of 40 GBit/s transimpedance amplifiers and a 80 GBit/s broadband amplifier demonstrate the efficiency of these methods.

Chapter 7 draws a conclusion and gives an outlook of future technical challenges in short-range optical communication systems.

Appendix A provides details and clarification about the notation and terminology used in this work. Appendix B discusses measurement techniques used for characterization of the presented circuits. Finally, Appendix C gives an overview about the used semiconductor technologies.